CPU缓存

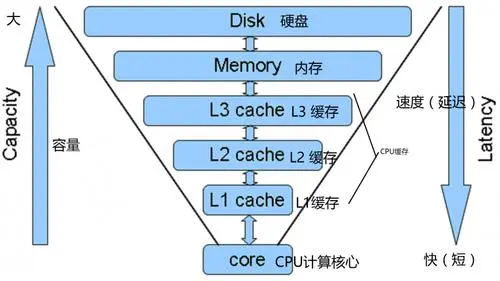

编辑CPU 缓存是计算机中央处理器 (CPU) 用来降低从主内存访问数据的平均成本(时间或能量)的硬件缓存。 高速缓存是更小、更快的内存,靠近处理器核心,它存储来自频繁使用的主内存位置的数据副本。 大多数 CPU 具有多个缓存级别(L1、L2,通常是 L3,很少甚至是 L4)的层次结构,在级别 1 具有不同的特定于指令和特定于数据的缓存。高速缓存通常使用静态随机存取存储器实现( SRAM),在现代 CPU 中,芯片面积占最大部分,但 SRAM 并不总是用于所有级别(I 缓存或 D 缓存),甚至任何级别,有时某些级别或所有级别都使用 动态随机存取存储器。

存在其他类型的缓存(不计入上述最重要缓存的缓存大小),例如转换后备缓冲区 (TLB),它是大多数 CPU 所具有的内存管理单元 (MMU) 的一部分。

概览

编辑当尝试读取或写入主内存中的某个位置时,处理器会检查来自该位置的数据是否已在高速缓存中。 如果是这样,处理器将读取或写入缓存而不是慢得多的主内存。

许多现代台式机、服务器和工业 CPU 至少具有三个独立的缓存:

Instruction cache用于加速可执行指令的获取;Data cache用于加速数据的获取和存储; 数据缓存通常组织为更多缓存级别的层次结构。转换后备缓冲区 (TLB) 用于加速两个可执行文件的虚拟到物理地址转换 指令和数据。 可以提供单个 TLB 来访问指令和数据,或者可以提供单独的指令 TLB (ITLB) 和数据 TLB (DTLB)。 但是,TLB 缓存是内存管理单元 (MMU) 的一部分,与 CPU 缓存没有直接关系。

历史

编辑CPU 存储的早期示例包括 Atlas 2 和 1960 年代的 IBM system/360 Model 85。 第一个使用缓存的 CPU 只有一级缓存; 与后来的 1 级缓存不同,它没有拆分为 L1d(用于数据)和 L1i(用于指令)。 SPlit L1 cache 始于 1976 年的 IBM 801 CPU,在 80 年代后期成为主流,并于 1997 年以 ARMv5TE 进入嵌入式 CPU 市场。 2015 年,甚至低于美元的 SoC 也拆分了 L1 缓存。 它们也有 L2 缓存,对于更大的处理器,还有 L3 缓存。 L2 缓存通常不拆分,并充当已拆分的 L1 缓存的公共存储库。 多核处理器的每个内核都有一个专用的 L1 缓存,通常不在内核之间共享。 L2 缓存和更高级别的缓存可以在内核之间共享。 L4 高速缓存目前并不常见,通常位于(一种形式的)动态随机存取存储器 (DRAM) 上,而不是位于静态随机存取存储器 (SRAM) 上,位于单独的芯片或芯片上(例外情况下,eDRAM 是 用于各级缓存,低至 L1)。 L1 在历史上也是如此,而更大的芯片允许集成它和通常所有缓存级别,最后一级可能除外。 每个额外的缓存级别往往更大并且优化不同。

缓存(如历史上的 RAM)的大小通常为:2、4、8、16 等 KiB 的幂; 当达到 MiB 大小时(即对于更大的非 L1),模式很早就崩溃了,以允许更大的缓存而不被迫进入大小加倍的范例,例如 2008 年 4 月,具有 3 MiB L2 缓存的 Intel Core 2 Duo。但是对于 L1 大小来说,这仍然只计入少量 KiB,但是 2012 年的 IBM zEC12 是一个例外,为其获得异常大的 96 KiB L1 数据缓存 时间,例如 IBM z13 具有 96 KiB L1 指令缓存(和 128 KiB L1 数据缓存),以及 2018 年基于英特尔 Ice Lake 的处理器,具有 48 KiB L1 数据缓存和 48 KiB L1 指令缓存。 2020 年,一些 Intel Atom CPU(最多 24 个内核)具有 4.5 MiB 和 15 MiB 的(倍数)缓存大小。

缓存条目

数据以固定大小的块(称为缓存行或缓存块)在内存和缓存之间传输。 当缓存行从内存复制到缓存中时,会创建一个缓存条目。 缓存条目将包括复制的数据以及请求的内存位置(称为标记)。

当处理器需要读取或写入内存中的某个位置时,它首先检查缓存中的相应条目。 高速缓存检查可能包含该地址的任何高速缓存行中请求的内存位置的内容。 如果处理器发现内存位置在高速缓存中,则发生了高速缓存命中。 但是,如果处理器在高速缓存中找不到内存位置,则发生了高速缓存未命中。 在缓存命中的情况下,处理器立即读取或写入缓存行中的数据。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/195845/