组合逻辑

编辑组合逻辑在自动机理论中,组合逻辑(也被称为时间无关的逻辑或组合逻辑)是一种数字逻辑,由布尔电路实现,其中输出仅是当前输入的纯函数。这与顺序逻辑相反,在顺序逻辑中,输出不仅取决于当前的输入,而且还取决于输入的历史。换句话说,顺序逻辑有记忆,而组合逻辑没有。组合逻辑在计算机电路中被用来对输入信号和存储数据进行布尔代数。实用的计算机电路通常包含组合逻辑和顺序逻辑的混合物。例如,算术逻辑单元(ALU)中进行数学计算的部分是用组合逻辑构成的。计算机中使用的其他电路,如半加器、全加器、半减器、全减器、多路复用器、解复用器、编码器和解码器也是使用组合逻辑制成。组合逻辑系统的实际设计可能需要考虑实际逻辑元件对其输入变化作出反应所需的有限时间。当一个输出是由几个不同的路径与不同数量的开关元件组合而成的结果时,输出可能会在最终状态之前暂时改变状态,因为这些变化沿着不同的路径传播。

组合逻辑的表示法

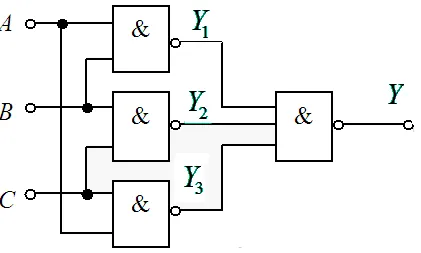

编辑组合逻辑用于构建从某些输入产生指定输出的电路。组合逻辑的构建一般使用两种方法之一:积的和,或和的积。考虑下面的真值表。使用乘积之和,将所有产生真实结果的逻辑语句相加,得出结果。使用布尔代数,结果可简化为以下等价的真值表。

逻辑公式最小化

编辑组合逻辑公式的最小化(简化)是根据布尔代数的规律,用以下规则完成的。通过使用最小化(有时称为逻辑优化),可以得出一个简化的逻辑函数或电路,逻辑组合电路变得更小,更容易分析、使用或构建。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/167681/