转译后备缓冲器

编辑转换后备缓冲区 (TLB) 是一种内存缓存,用于存储虚拟内存到物理内存的最新转换。 它用于减少访问用户内存位置所花费的时间。 它可以称为地址转换缓存。 它是芯片内存管理单元 (MMU) 的一部分。 TLB 可能驻留在 CPU 和 CPU 高速缓存之间、CPU 高速缓存和主内存之间或多级高速缓存的不同级别之间。 大多数台式机、笔记本电脑和服务器处理器在内存管理硬件中包含一个或多个 TLB,并且它几乎总是存在于任何使用分页或分段虚拟内存的处理器中。

TLB 有时被实现为内容可寻址存储器 (CAM)。 CAM搜索关键字是虚拟地址,搜索结果是物理地址。 如果请求的地址存在于 TLB 中,CAM 搜索会快速产生匹配,并且检索到的物理地址可用于访问内存。 这称为 TLB 命中。 如果请求的地址不在 TLB 中,则为未命中,转换通过在称为页遍历的过程中查找页表来进行。 与处理器速度相比,页面遍历非常耗时,因为它涉及读取多个内存位置的内容并使用它们来计算物理地址。 通过页面遍历确定物理地址后,将虚拟地址到物理地址的映射输入到 TLB 中。 例如,PowerPC 604 有一个用于数据加载和存储的双向集关联 TLB。 一些处理器具有不同的指令和数据地址 TLB。

概览

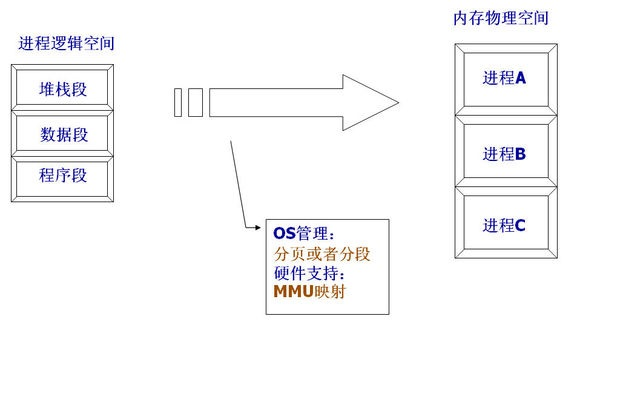

编辑TLB 有固定数量的槽,其中包含页表条目和段表条目; 页表条目将虚拟地址映射到物理地址和中间表地址,而段表条目将虚拟地址映射到段地址、中间表地址和页表地址。 虚拟内存是从一个进程来看的内存空间; 这个空间通常被分成固定大小的页面(在分页内存中),或者不太常见地分成可变大小的段(在分段内存中)。 页表通常存储在主内存中,它跟踪虚拟页面在物理内存中的存储位置。 此方法使用两次内存访问(一次用于页表条目,一次用于字节)来访问一个字节。 首先,在页表中查找帧号。 其次,带有页面偏移量的帧号给出了实际地址。 因此,任何直接的虚拟内存方案都会使内存访问时间加倍。 因此,TLB 用于减少访问页表方法中的内存位置所花费的时间。 TLB 是页表的缓存,仅代表页表内容的一个子集。

参考物理内存地址,TLB 可能驻留在 CPU 和 CPU 高速缓存之间、CPU 高速缓存和主存储内存之间或多级高速缓存的级别之间。 放置决定了缓存是使用物理寻址还是虚拟寻址。 如果缓存被虚拟寻址,请求直接从 CPU 发送到缓存,只有在缓存未命中时才会访问 TLB。 如果缓存是物理寻址的,CPU 会在每次内存操作时进行 TLB 查找,并将得到的物理地址发送到缓存。

在哈佛架构或修改后的哈佛架构中,指令和数据可能存在单独的虚拟地址空间或内存访问硬件。 这可能导致每种访问类型都有不同的 TLB,即指令转换后备缓冲区 (ITLB) 和数据转换后备缓冲区 (DTLB)。 单独的数据和指令 TLB 已经证明了各种好处。

TLB 可用作快速查找硬件缓存。 该图显示了 TLB 的工作。 TLB 中的每个条目都由两部分组成:标记和值。 如果传入虚拟地址的标签与TLB中的标签匹配,则返回相应的值。 由于 TLB 查找通常是指令流水线的一部分,因此搜索速度很快并且基本上不会造成性能损失。

然而,为了能够在指令流水线内进行搜索,TLB 必须很小。

物理寻址高速缓存的常见优化是在高速缓存访问的同时执行 TLB 查找。 在每次访问虚拟内存时,硬件都会检查 TLB 以查看页码是否保存在其中。 如果是,则为 TLB 命中,并进行翻译。 返回帧号并用于访问内存。 如果页码不在 TLB 中,则必须检查页表。 根据 CPU,这可以使用硬件或使用操作系统中断自动完成。 得到帧号后,就可以用来访问内存了。 此外,我们将页码和帧号添加到 TLB 中,以便在下次引用时快速找到它们。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/195864/