指令级并行

编辑指令级并行 (ILP) 是计算机程序中指令序列的并行或同时执行。 更具体地说,ILP 是指此并行执行中每步运行的平均指令数。

讨论

编辑ILP 不能与并发相混淆。 在 ILP 中,进程有一个特定的执行线程。 另一方面,并发涉及将多个线程严格交替分配给 CPU 的核心,或者如果有足够的 CPU 核心,则以真正的并行方式分配,理想情况下每个可运行线程一个核心。

指令级并行有两种方法:硬件和软件。

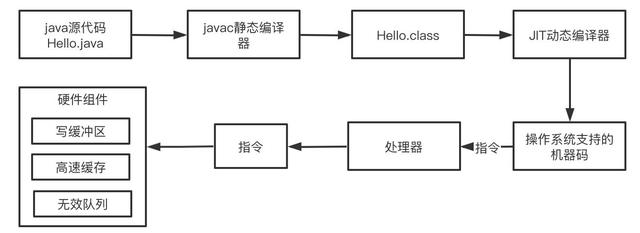

硬件级别工作在动态并行性上,而软件级别工作在静态并行性上。 动态并行意味着处理器在运行时决定并行执行哪些指令,而静态并行意味着编译器决定并行执行哪些指令。 奔腾处理器在并行执行的动态序列上工作,而安腾处理器在静态级并行上工作。

考虑以下程序:

e = a + bf = c + dm = e * f

操作 3 取决于操作 1 和操作 2 的结果,因此必须在它们都完成后才能计算。 但是,操作 1 和 2 不依赖于任何其他操作,因此可以同时计算它们。 如果我们假设每个操作可以在一个时间单位内完成,那么这三个指令总共可以在两个时间单位内完成,ILP 为 3/2。

编译器和处理器设计人员的目标是尽可能多地识别和利用 ILP。 普通程序通常是在顺序执行模型下编写的,其中指令一条接一条地执行,并按照程序员指定的顺序执行。 ILP 允许编译器和处理器重叠执行多条指令,甚至可以改变指令执行的顺序。

程序中存在多少 ILP 是非常特定于应用程序的。 在某些领域,例如图形和科学计算,数量可能非常大。 然而,密码学等工作负载可能表现出更少的并行性。

- 指令流水线,多条指令的执行可以部分重叠。

- 超标量执行、VLIW 以及密切相关的显式并行指令计算概念,其中多个执行单元用于并行执行多条指令。

- 乱序执行,其中指令以不违反数据依赖性的任何顺序执行。 请注意,此技术独立于流水线和超标量执行。 当前动态乱序执行的实现(即,当程序正在执行并且没有编译器的任何帮助时)从普通程序中提取 ILP。 另一种方法是在编译时提取这种并行性,并以某种方式将此信息传递给硬件。 由于扩展乱序执行技术的复杂性,业界重新审视了指令集,这些指令集明确编码每条指令的多个独立操作。

- 寄存器重命名是指一种技术,用于避免因这些操作重用寄存器而强加的不必要的程序操作序列化,用于实现乱序执行。

- 推测执行,允许在确定是否应该执行之前执行完整指令或部分指令。 一种常用的推测执行形式是控制流推测,其中在确定控制流指令的目标之前执行通过控制流指令(例如,分支)的指令。 已经提出并正在使用其他几种形式的推测执行,包括由值预测、内存依赖性预测和缓存延迟预测驱动的推测执行。

- 分支预测,用于避免拖延以解决控制依赖性。 分支预测与推测执行一起使用。

众所周知,编译器和硬件支持都利用了 ILP,但编译器还通过编译时优化为硬件提供了程序中固有和隐式的 ILP。 用于在程序中提取可用 ILP 的一些优化技术包括指令调度、寄存器分配/重命名和内存访问优化。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/196071/