层叠式封装

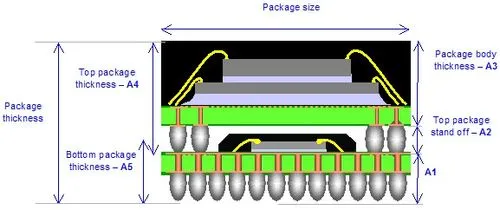

编辑层叠式封装 (PoP) 是一种将分立逻辑和存储球栅阵列 (BGA) 封装垂直组合的集成电路封装方法。 两个或多个封装安装在彼此之上,即堆叠,并使用标准接口在它们之间路由信号。 这允许在移动电话、个人数字助理 (PDA) 和数码相机等设备中实现更高的组件密度,但代价是高度要求略高。 出于散热考虑,具有 2 个以上封装的堆栈并不常见。

配置

编辑PoP 存在两种广泛使用的配置:

- 纯内存堆叠:两个或多个纯内存封装相互堆叠

- 混合逻辑-内存堆叠:逻辑 (CPU) 封装在底部,内存封装在顶部。 例如,底部可能是手机的片上系统 (SoC)。 逻辑封装位于底部,因为它需要更多的 BGA 连接到主板。

在 PCB 组装过程中,PoP 堆叠的底部封装直接放置在 PCB 上,堆叠的其他封装堆叠在顶部。PoP 堆叠的封装相互连接(并连接到 PCB) 在回流焊期间。

好处

编辑封装技术试图将传统封装的优点与芯片堆叠技术的优点结合起来,同时避免它们的缺点。

传统封装将每个芯片放置在自己的封装中,这种封装专为普通 PCB 组装技术而设计,可将每个封装并排直接放置在 PCB 上。3D 芯片堆叠系统级封装 (SiP) 技术将多个芯片堆叠在单个芯片中 封装,与传统的 PCB 组装相比,它有几个优点,也有一些缺点。

相对于传统隔离芯片封装的优势

编辑最明显的好处是节省主板空间。 PoP 使用的 PCB 面积要少得多,几乎与堆叠芯片封装一样少。

在电气方面,PoP 通过最小化不同互操作部件(例如控制器和内存)之间的轨道长度来提供优势。 这会产生更好的器件电气性能,因为电路之间互连的较短路由会产生更快的信号传播并减少噪声和串扰。

相对芯片堆叠的优势

编辑堆叠芯片和堆叠封装产品之间存在几个关键差异。

封装上封装的主要经济利益是存储器件与逻辑器件分离。 因此,这为 PoP 提供了传统封装优于堆叠芯片产品的所有相同优势:

- 内存包可以和逻辑包分开测试

- 在最后的组装中只使用已知的好包(如果内存坏了,只有内存被丢弃等等)。 将其与堆叠裸片封装进行比较,如果内存或逻辑有问题,整组芯片都无用并被拒绝。

- 最终用户(例如手机或数码相机制造商)控制物流。 这意味着来自不同供应商的内存可以在不同的时间使用,而无需改变逻辑。 内存成为一种商品,可以从成本最低的供应商处采购。 与 PiP(封装中封装)相比,此特性也是一个优势,后者需要在最终用户的上游设计和采购特定的存储设备。

- 可以使用任何机械匹配的顶部封装。 对于低端手机,顶层封装可能会使用较小的内存配置。 对于高端手机,同样的底层封装可以使用更多的内存。 这简化了 OEM 的库存控制。 对于堆叠芯片封装甚至 PiP(封装中封装),必须提前几周或几个月知道确切的内存配置。

- 因为内存只在最后组装时才进入混合,所以逻辑供应商没有理由采购任何内存。 对于堆叠芯片设备,逻辑提供商必须从内存供应商处购买内存晶圆。

-

JEDEC 标准化

编辑- JEDEC JC-11 委员会处理与底部 PoP 封装相关的封装外形图标准。

- JEDEC JC-63 委员会处理顶级(内存)PoP 封装引出线标准化。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/242818/