动态逻辑(数字电子学)

编辑在集成电路设计中,动态逻辑(或有时是时钟逻辑)是组合逻辑电路的一种设计方法,特别是那些用MOS技术实现的电路。它区别于所谓的静态逻辑,因为它利用了杂散电容和门电容中的临时信息存储。它在20世纪70年代很流行,最近在高速数字电子技术,特别是计算机CPU的设计中出现了回潮。动态逻辑电路通常比静态同类电路更快,所需的表面积更小,但设计起来更困难。动态逻辑比静态逻辑有更高的切换率,但被切换的电容负载更小,所以动态逻辑的整体功耗可能更高,也可能更低,这取决于各种权衡。当提到一个特定的逻辑系列时,动态形容词通常足以区分设计方法,例如动态CMOS或动态SOI设计。动态逻辑与所谓的静态逻辑的区别在于,动态逻辑在实现组合逻辑电路时使用时钟信号。时钟信号的通常用途是使顺序逻辑电路中的转换同步化。对于大多数组合逻辑的实现,甚至不需要时钟信号。用来指代组合电路的静态/动态术语不应该与同样的形容词用于区分存储器件的方式相混淆,例如静态RAM和动态RAM。

动态逻辑(数字电子学)的术语

编辑在逻辑设计的背景下,与时钟逻辑相比,动态逻辑这个术语更常用,因为它明确了这种设计与静态逻辑之间的区别。为了进一步混淆视听,时钟逻辑有时被用作顺序逻辑的同义词。这种用法是不标准的,应该避免。

静态与动态逻辑

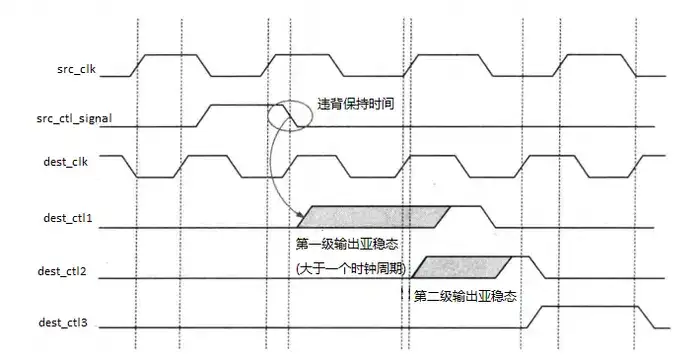

编辑静态与动态逻辑的最大区别是,在动态逻辑中,时钟信号被用来评估组合逻辑。在大多数类型的逻辑设计中,称为静态逻辑,任何时候都有一些机制来驱动输出,要么是高电平,要么是低电平。在许多流行的逻辑风格中,如TTL和传统的CMOS,这一原则可以重新表述为:在输出和电源电压或地之间始终有一个低阻抗的直流路径。顺便提一下,在高阻抗输出的情况下,这个定义当然有一个例外,比如三态缓冲器;但是,即使在这些情况下,电路也是为了在一个更大的系统中使用,在这个系统中,一些机制将驱动输出,它们并不符合与静态逻辑不同的条件。相反,在动态逻辑中,并不总是有一个机制来驱动输出的高或低。在这个概念的最常见版本中,输出在时钟周期的不同部分被驱动为高电平或低电平。在输出没有被主动驱动的时间间隔内,杂散电容使其保持在驱动水平的某个公差范围内。动态逻辑需要一个足够快的最低时钟速率,以便在输出电容中的电荷泄漏到足以导致输出的数字状态改变之前,每个动态门的输出状态被使用或刷新,在输出未被主动驱动的时钟周期的部分。静态逻辑没有最小的时钟速率–时钟可以无限期地暂停。虽然看起来长时间什么都不做并不是特别有用,但它有三个优点。能够在任何时候暂停系统使调试和测试更加容易,使单步等技术成为可能。能够在极低的时钟速率下运行系统,使低功耗电子器件在特定的电池上运行更长时间。一个完全静态的系统可以立即恢复到它离开的地方;人们不必等待系统启动或恢复。

能够在任何时候暂停系统的任何时间,也可以用来使CPU与一个异步事件同步。虽然有其他机制可以做到这一点,如中断、轮询循环、处理器空闲输入引脚(例如6502上的RDY),或处理器总线周期扩展机制,如WAIT输入,但使用硬件对静态内核CPU的时钟进行门控更简单,时间上更精确,不使用程序代码内存,并且在等待时几乎不使用CPU的功率。在一个基本的设计中,为了开始等待,CPU将写入一个寄存器来设置一个二进制锁存位,该锁存位将与处理器时钟相加或相乘,使处理器停止工作。一个来自外围设备的信号将重置这个锁存器,恢复CPU的操作。硬件逻辑必须对锁存器控制输入进行必要的门控,以确保锁存器的输出转换不会导致时钟信号电平的瞬间变化,并导致时钟脉冲,无论是高电平还是低电平,都要短一些。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/171059/