- 1 集成注入逻辑

集成注入逻辑

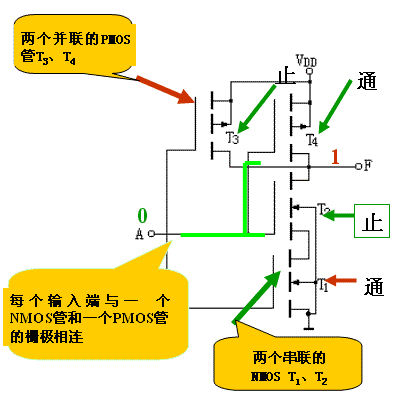

编辑集成注入逻辑是一类用多集电极双极结晶体管(BJT)构建的数字电路。在推出时,它的速度可与TTL相媲美,但几乎与CMOS一样低功率,使其成为VLSI(和更大)集成电路的理想选择。由于不需要互补晶体管,用这种逻辑系列的门可以做得比CMOS小。虽然逻辑电压水平非常接近,但I2L具有很高的抗噪声能力,因为它是通过电流而不是电压工作的。这种逻辑系列的一个缺点是,与CMOS不同,门在不开关时要耗电。结构I2L反相器门由一个PNP共基电流源晶体管和一个NPN共发射极集电极开路反相器晶体管构成(即它们都连接到GND)。在一个晶圆上,这两个晶体管被合并。

一个小电压(约1伏)被提供给电流源晶体管的发射极,以控制提供给反相晶体管的电流。晶体管被用于集成电路的电流源,因为它们比电阻小得多。因为反相器是集电极开路的,所以可以通过将两个或更多门的每个输出连接在一起来进行有线的AND操作。因此,以这种方式使用的输出的扇出是一个。然而,通过向反相器晶体管添加更多的集电极,可以产生额外的输出。栅极的构造非常简单,只需一层互连的金属即可。

在I2L电路的分立实现中,具有多个集电极的双极NPN晶体管可以用多个分立的3端NPN晶体管代替,这些晶体管的基极连接在一起,发射极也同样连接在一起。电流源晶体管可以用一个从正电源到逆变晶体管基极的电阻来代替,因为分立的电阻比分立的晶体管更小,更便宜。同样,合并的PNP电流注入器晶体管和NPN反相器晶体管也可以作为独立的分立元件来实现。

操作I2L电路的核心是共射极开集电极反相器。通常情况下,反相器由一个NPN晶体管组成,发射极连接到地,基极由电流源提供的正向电流偏置。输入端以电流灌注器(低逻辑电平)或高Z浮动状态(高逻辑电平)的形式提供给基极。逆变器的输出在集电极上。同样,它要么是一个电流灌注器(低逻辑电平),要么是一个高z浮动条件(高逻辑电平)。像直接耦合的晶体管逻辑一样,在一个NPN晶体管的输出(集电极)和下面一个晶体管的输入(基极)之间没有电阻。为了理解反相器的工作原理,有必要了解电流的流动。如果偏置电流被分流到地(低逻辑电平),晶体管会关闭,集电极浮动(高逻辑电平)。

如果偏置电流没有被分流到地,因为输入是高Z(高逻辑电平),偏置电流通过晶体管流向发射极,接通晶体管,并允许集电极沉降电流(低逻辑电平)。由于反相器的输出可以灌入电流,但不能灌入电流,因此将多个反相器的输出连接在一起,形成一个有线的AND门是安全的。

由于晶体管的内部寄生电容,更高的电流流入反相晶体管的基极,导致更快的开关速度,而且由于I2L的高低逻辑电平之间的电压差比其他双极逻辑系列要小(大约0.5伏,而不是大约3.3或5伏),由于充电和放电的寄生电容造成的损失被最小化。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/171072/