通路晶体管逻辑

编辑在电子学中,通路晶体管逻辑(PTL)描述了集成电路设计中使用的几个逻辑系列。它通过消除多余的晶体管,减少了用于制造不同逻辑门的晶体管的数量。晶体管被用作开关,在电路的节点之间传递逻辑电平,而不是作为直接连接到电源电压的开关。这减少了有源器件的数量,但有一个缺点,即高低逻辑电平之间的电压差在每个阶段都会减少。每个串联的晶体管在其输出端比其输入端饱和度低。如果在一个逻辑路径中串联了几个器件,可能需要一个传统结构的门来将信号电压恢复到满值。相比之下,传统的CMOS逻辑开关晶体管,使输出连接到电源的一个轨道(类似于集电极开路方案),所以顺序链中的逻辑电压水平不会下降。可能需要对电路进行模拟以确保足够的性能。

通路晶体管逻辑的应用

编辑晶体管逻辑通常使用更少的晶体管,运行速度更快,并且比用完全互补的CMOS逻辑中的相同晶体管实现的相同功能所需的功率更小。XOR具有最坏的Karnaugh图–如果从简单门实现,它需要比其他功能更多的晶体管。Z80和许多其他芯片的设计者通过使用通晶体管逻辑而不是简单门实现XOR,节省了一些晶体管。

通式晶体管电路的基本原理

编辑通式晶体管由一个周期性的时钟信号驱动,作为一个接入开关,根据输入信号Vin,对寄生电容Cx进行充电或降压。因此,有两种可能的操作,当时钟信号是有效的(CK=1)是逻辑1的转移(将电容Cx充电到逻辑高电平)和逻辑0的转移(将电容Cx充电到逻辑低电平)。在这两种情况下,耗尽型负载nMOS反相器的输出显然是一个逻辑低电平或逻辑高电平,这取决于电压Vx。互补式通透晶体管逻辑一些作者使用互补式通透晶体管逻辑这一术语来表示一种实现逻辑门的方式,即使用由NMOS和PMOS通透晶体管组成的传输门。

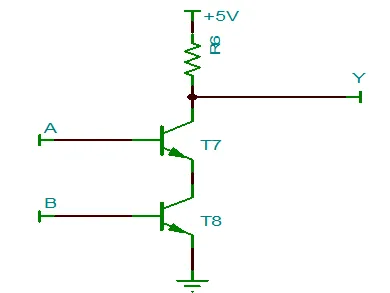

其他作者使用术语互补通透晶体管逻辑(CPL)来表示一种实现逻辑门的方式,其中每个门由一个仅有NMOS的通透晶体管网络组成,然后是一个CMOS输出反相器。其他作者使用术语”互补通过晶体管逻辑(CPL)”来表示一种使用双轨编码的逻辑门的实现方式。每个CPL门都有两根输出线,都是正信号和互补信号,不需要反相器。互补通过晶体管逻辑或差分通过晶体管逻辑是指为某些优势而设计的逻辑家族。在多路复用器和锁存器中使用这种逻辑系列很常见。CPL使用串联晶体管在逻辑的可能反转输出值之间进行选择,其输出驱动反相器。CMOS传输门由并联的nMOS和pMOS晶体管组成。

其他形式

编辑存在静态和动态类型的传递晶体管逻辑,在速度、功率和低电压操作方面具有不同的特性。随着集成电路电源电压的降低,通过晶体管逻辑的缺点变得更加显著;与电源电压相比,晶体管的阈值电压变得很大,严重限制了顺序级的数量。因为通常需要互补输入来控制通断晶体管,所以需要额外的逻辑级。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/171085/