时间门控

编辑时钟门控是许多同步电路中用于降低动态功耗的流行技术,方法是在电路不使用或忽略时钟信号时移除时钟信号。 时钟门控通过修剪时钟树来节省功耗,但代价是向电路中添加更多逻辑。 修剪时钟会禁用部分电路,以便其中的触发器不必切换状态。 切换状态消耗功率。 不开关时,开关功耗为零,只产生漏电流。

尽管根据定义,异步电路没有全局时钟,但术语完美时钟门控用于说明各种时钟门控技术如何简单地近似异步电路所表现出的数据相关行为。 随着同步电路时钟门控的粒度接近于零,该电路的功耗接近异步电路的功耗:电路仅在主动计算时产生逻辑转换。

详情

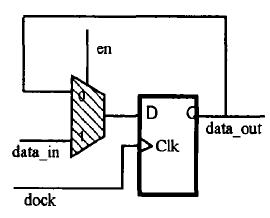

编辑时钟门控的替代解决方案是在采用输入多路复用器的同步数据路径上使用时钟启用 (CE) 逻辑,例如,对于 D 型触发器:使用 C/Verilog 语言符号:Dff= CE? D:问; 其中:Dff为D型触发器的D输入,D为模块信息输入(无CE输入),Q为D型触发器输出。 这种类型的时钟门控是无竞争条件的,是 FPGA 设计和小型电路的时钟门控的首选。 对于 FPGA,每个 D 型触发器都有一个额外的 CE 输入信号。

时钟门控通过获取附加到寄存器的启用条件来工作,并使用它们来门控时钟。 设计必须包含这些使能条件才能使用时钟门控并从中受益。 这个时钟门控过程还可以节省大量的管芯面积和功耗,因为它去除了大量的多路复用器并用时钟门控逻辑取而代之。 这种时钟门控逻辑通常采用集成时钟门控 (ICG) 单元的形式。 然而,时钟门控逻辑将改变时钟树结构,因为时钟门控逻辑将位于时钟树中。

可以通过多种方式将时钟门控逻辑添加到设计中:

- 作为启用条件编码到寄存器传输级 (RTL) 代码中,可以通过综合工具(细粒度时钟门控)自动转换为时钟门控逻辑。

- 由 RTL 设计人员手动插入到设计中(通常作为模块级时钟门控),方法是实例化库特定的集成时钟门控 (ICG) 单元以门控特定模块或寄存器的时钟。

- 通过自动时钟门控工具半自动插入 RTL。 这些工具要么将 ICG 单元插入到 RTL 中,要么将启用条件添加到 RTL 代码中。 这些通常还提供顺序时钟门控优化。

任何用于改进时钟门控的 RTL 修改都会导致设计的功能更改(因为寄存器现在将保存不同的值),这需要进行验证。

顺序时钟门控是将启用条件提取/传播到上游/下游顺序元件的过程,以便可以对其他寄存器进行时钟门控。

旨在使用电池或以非常低的功率运行的芯片(例如手机、可穿戴设备等中使用的芯片)将同时实施多种形式的时钟门控。 一方面是通过软件手动门控时钟,其中驱动程序启用或禁用给定空闲控制器使用的各种时钟。 另一端是自动时钟门控,可以告诉硬件检测是否有任何工作要做,如果不需要则关闭给定的时钟。 这些表单相互交互,并且可能是同一启用树的一部分。 例如,内部桥接器或总线可能使用自动门控,以便在 CPU 或 DMA 引擎需要使用它之前关闭它,而该总线上的一些外设如果在该板上未使用,则可能会永久关闭 .。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/195648/