双倍数据速率

编辑在计算中,以双倍数据速率 (DDR) 运行的计算机总线在时钟信号的上升沿和下降沿传输数据。 这也称为双泵、双泵和双过渡。 在 NAND 闪存的上下文中使用术语切换模式。

概览

编辑设计时钟电子电路的最简单方法是让它在时钟信号的每个完整周期(上升和下降)执行一次传输。 然而,这要求时钟信号每次传输更改两次,而数据线每次传输最多更改一次。 在高带宽下运行时,信号完整性限制会限制时钟频率。 通过使用时钟的两个边沿,数据信号以相同的限制频率运行,从而使数据传输速率加倍。

此技术已用于微处理器前端总线、Ultra-3 SCSI、扩展总线(AGP、PCI-X)、图形内存 (GDDR)、主内存(RDRAM 和 DDR1 到 DDR5)以及 AMD 上的 HyperTranSPort 总线 ‘s Athlon 64 处理器。 它最近被用于具有高数据传输速度要求的其他系统——例如,用于模数转换器 (ADC) 的输出。

不要将 DDR 与双通道混淆,双通道中每个内存通道同时访问两个 RAM 模块。 这两种技术相互独立,许多主板通过在双通道配置中使用 DDR 内存来同时使用这两种技术。

双泵或四泵的替代方法是使链路自计时。 InfiniBand 和 PCI Express 选择了这种策略。

带宽与频率的关系

编辑描述双泵总线的带宽可能会令人困惑。 每个时钟边沿称为一个节拍,每个周期有两个节拍(一个正拍和一个负拍)。 从技术上讲,赫兹是每秒周期数的单位,但很多人指的是每秒传输的次数。 谨慎使用通常会谈论 500 MHz、双倍数据速率或 1000 MT/s,但许多人随便指的是 1000 MHz 总线,即使没有比 500 MHz 更快的信号周期。

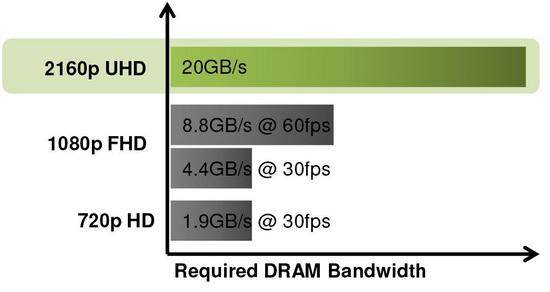

DDR SDRAM 普及了以兆字节/秒为单位表示总线带宽的技术,即传输速率和以字节为单位的总线宽度的乘积。 以 100 MHz 时钟运行的 DDR SDRAM 称为 DDR-200(以其 200 MT/s 的数据传输速率命名),以该数据速率运行的 64 位(8 字节)宽 DIMM 称为 PC-1600,以其命名 1600 MB/s 峰值(理论)带宽。 同样,传输速率为 12.8 GB/s 的 DDR3-1600 称为 PC3-12800。

DDR 模块常用名称的一些示例:

DDR SDRAM 仅在数据线上使用双倍数据速率信号。 地址和控制信号仍然在每个时钟周期(准确地说,在时钟的上升沿)发送一次到 DRAM,并且 CAS 延迟等时序参数以时钟周期指定。 一些不太常见的 DRAM 接口,特别是 LPDDR2、GDDR5 和 XDR DRAM,使用双倍数据速率发送命令和地址。 DDR5 使用两个 7 位双倍数据速率命令/地址总线连接到每个 DIMM,其中注册时钟驱动器芯片将转换为每个内存芯片的 14 位 SDR 总线。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/195659/