SDRAM

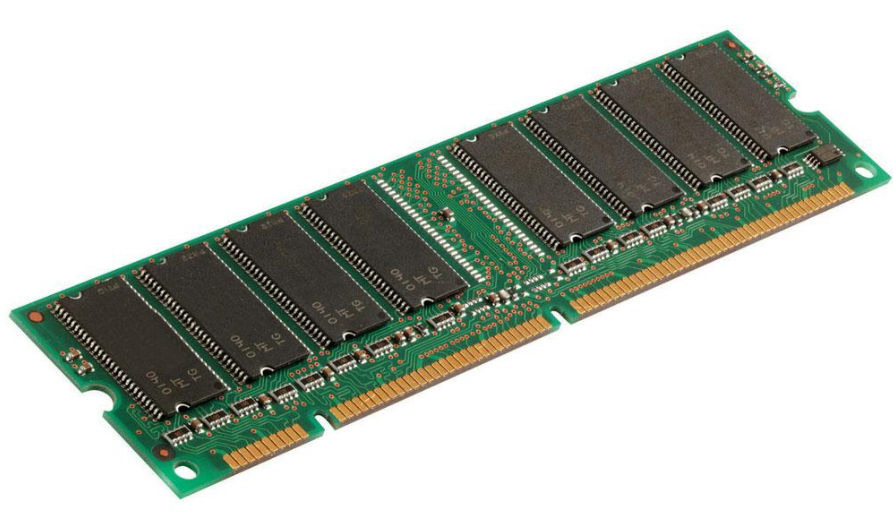

编辑SDRAM是一种半导体存储器变体,例如用作计算机中的主存储器。

缩写SDRAM也可以指装有SDRAM芯片的DIMM或SO-DIMM印刷电路板。

SDRAM 是一种时钟 DRAM 技术。 时钟由系统总线指定,也可能由连接到系统总线的单独内存总线指定。 使用用于地址输入、控制信息和输入/输出数据的寄存器进行计时,因为寄存器中的值更改仅在时钟沿发生。 使用时钟进行同步消除了使用异步方法(例如使用握手方法)进行通信的需要。 此外,可以通过使用寄存器来使用缓冲和流水线技术,从而在时间上有显着的整体增益。 SDRAM 的速度大约是其前身 EDO-DRAM 的两倍。 第一代 SDRAM 模块在 1996 年至 2001 年左右用于 PC。 然后它被 DDR-SDRAM 取代,在 DDR-SDRAM 中,通过使用两个时钟边沿,数据速率几乎可以翻倍。

不同类型

编辑常见的RAM类型有:

- PC-66-SDRAM:Intel 定义的标准,其中 SDRAM 的理想运行速度为 66 MHz。 焊接的存储芯片的访问时间为 12 ns(很少)或 10 ns。

- PC-100 SDRAM:Intel 定义的标准,其中 SDRAM 的理想运行速度为 100 MHz,向后兼容 PC-66 主板(可以在 66 MHz 下运行)。 焊接的存储芯片的访问时间为 8 ns。

- PC-133-SDRAM:随着前端总线的时钟频率增加到133MHz,威盛推出了以相同速度运行的PC-133-SDRAM,以充分利用时钟增加的速度优势. 向后兼容 PC-66/-100 主板(可以运行在 66MHz 或 100MHz)。 焊接的存储芯片的访问时间为 7.5 ns(芯片上很少标记为 -7.5,但通常有点刺激 -75)或 7.0 ns。

- PC-150/166-SDRAM:功能特别强大的 SDRAM,可以在指定的 MHz 范围内运行,具体取决于制造商。

负责的 JEDEC 委员会已将 PC-66、PC-100 和 PC-133 指定为标准。 相比之下,PC-150 和 PC-166 模块只是超频的 PC-133 模块,制造商已批准分别在 150 和 166 MHz 下运行。

SDRAM 模块的存储容量为 16 MiB、32 MiB、64 MiB、128 MiB、256 MiB、512 MiB 和 1024 MiB(很少); 每个 DIMM 大多使用四个、八个或十六个芯片。 16 MiB 模块实际上仅作为单面模块被发现,32 MiB 和 1024 MiB 模块实际上仅作为双面模块出现。 所有其他尺寸均可用作单面和双面模块。

还有一些模块的 CAS 延迟为二分之一 (CL2) 和三分之一 (CL3),后者的工作速度稍慢。 CL3 模块通常还允许以较低的时钟频率与 CL2 一起运行。 合适的 PC-100-CL3 模块可以与 CL2 一起运行,最大时钟频率高达 66 MHz,相应的 PC-133-CL3 模块与 CL2 一起运行,最大时钟频率高达 100 MHz。 PC-133-CL2 模块大多配备存取时间为 7.0 ns 的存储芯片。

缓冲/非缓冲 SDRAM

与内存容量较小的 SDRAM DIMM 相比,内存容量大的 SDRAM DIMM 具有大量存储单元和当今常见的高时钟速率,因此会在地址和控制线上造成更高的电容和电感负载。 因此,一些电路板设计人员在 SDRAM DIMM 模块上放置了双驱动器缓冲器,以增强线路上的信号并降低系统负载,与具有这些额外输出缓冲器的其他相同内存模块相比。 这个缓冲区 v但是,在电脉冲中引入了一个小的时间延迟,因此与具有输出缓冲器的同一模块相比,将此类缓冲器添加到没有缓冲器的正常填充模块会导致信号变慢。 这是一种技术,也主要用于服务器领域,以增加系统板(主板)上最大可能的 RAM 大小。

工作电压

编辑SDRAM 内存芯片需要 3.3 V 的工作电压。

兼容性问题

编辑较新的 PC133 模块可能与支持 SDRAM 的早期内存控制器不兼容。 因此,尽管 DIMM 的总内存容量仍在芯片组或主板规格范围内,但较新的 PC133 模块无法在较旧的主板上正常工作。 一个典型的例子是带有威盛 Apollo MVP3 芯片组的 Super Socket 7 主板上的 256 MiB PC 133 模块。 虽然较旧的 DIMM(两侧均配备八个 128-Mibit 芯片)在此类主板上正常工作,但较新的 256-MiB 内存模块(一侧仅配备八个 256-Mibit 芯片)无法工作或仅被识别为128-MiB DIMM。 除了内存密度之外,所用 SDRAM 芯片的不利内部组织也会削弱与内存控制器的兼容性。 512-MiB 和 1024-MiB 模块在带有威盛 Apollo MVP3 芯片组的主板上根本无法工作。 原因之一可能是并行存储单元过多导致容性负载过高,这会使驱动器不堪重负并导致软时钟边沿。

技术进步

编辑如果在正时钟沿和负时钟沿都可以更改值,则称为 DDR-SDRAM(双倍数据速率 SDRAM)。 DDR-SDRAM代表了SDRAM技术的进一步发展,为了明确语言,第一代SDRAM技术现在也称为SDR-SDRAM(单数据速率SDRAM)。 虽然 SDR SDRAM DIMM 只有 168 个针脚,但 DDR SDRAM 模块已经有 184 个针脚。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/372544/