高带宽存储器

编辑高带宽存储器,是AMD与SK海力士共同开发的宽带接口,用于在芯片级连接更大容量的动态内存(8至64 GB),以高传输速率传输图形或主处理器。

结构与技术

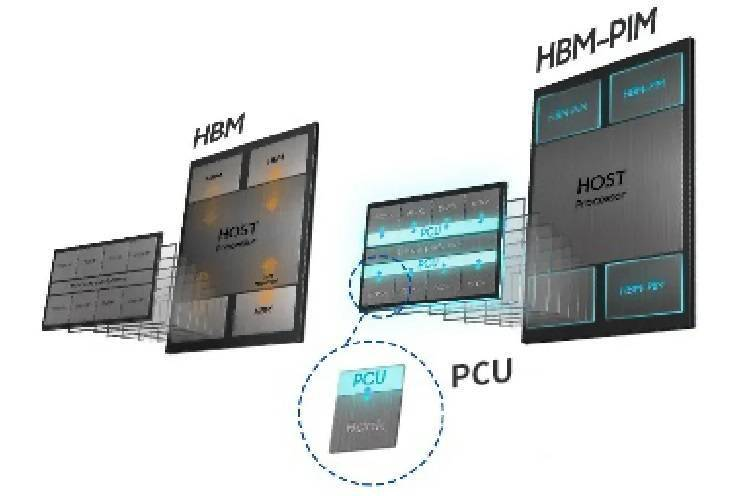

编辑与“普通”RAM 相比,HBM 接口更宽,连接不是通过连接器(计算机的主存储器)或在主电路板上进行的,而是通过由硅制成的施加器。 触点之间的距离为 40 至 100 µm,因此比“普通”电路中的 BGA 引脚密度高 5 倍。 每个引脚的数据速率在普通内存的范围内,并且比显卡内存慢。 高数据速率是通过大量数据引脚和每个引脚适中的数据速率实现的。

人体模型1

HBM 是一种存储技术,可以使多个裸片相互堆叠并并行连接。 该接口用于内存和 CPU、GPU 和 FPGA 之间。

在第一个应用中,堆叠了 4 个 1 GB 的 DRAM 模块。 该堆栈使用所谓的插入器与 CPU 或 GPU 建立比之前作为标准安装的 GDDR5 内存更快的连接。 总线宽度为每个堆栈 1024 条数据线。 内存时钟频率为 500MHz,数据在上升沿和下降沿 (DDR) 传输。 这些 HBM 堆栈中的多达四个与 CPU 或 GPU 一起被撞到插入器上,并且整个单元连接到电路板。 由于总线宽度大,总数据吞吐量达到每秒 0.5TB。

尽管这些 HBM 堆栈并未物理集成到 CPU 或 GPU 中,但它们通过具有极短电缆路径的中介层快速连接到那里,因此 HBM 的特性与片上 RAM 几乎没有区别。

HBM 显存的功耗也低于 GDDR5。 AMD 表示,HBM 提供的每瓦内存带宽是其三倍多。

HBM 需要的电路板面积比 GDDR5 小得多,这有利于构建具有高性能图形的笔记本电脑或平板电脑。 图形处理器上非常靠近的位置还允许图形芯片和 RAM 被一个相对较小的散热器覆盖。 但是,特别是下方的芯片只能在有限的范围内散热。

人体模型2

2016 年 1 月 12 日,HBM 2 被 JEDEC 接受为 JESD235a。

HBM 2 允许将多达 8 个裸片堆叠在一起,使内存吞吐量翻倍,每个裸片堆叠高达 100GB/s。 堆栈的大小范围为 1 到 8 GiB,允许最大扩展 32 GiB。 SK 海力士和三星都发布了 4GiB 堆栈。

HBM2 自 2016 年起用于 Nvidia Tesla 显卡,自 2017 年起用于 NVIDIA Quadro 显卡,自 2017 年年中起用于 AMD Radeon Vega 系列。

HBM 2E

2019 年 8 月 13 日推出,每个堆栈的最大容量翻倍,数据速率提高 50%。 内存制造商三星、SK 海力士和美光已插入 HBM 2E 作为过渡步骤,以便将容量翻倍并提高 HBM2 的 256 GB/s 传输速率,而无需等待 HBM3。

人体模型3

就像 HBM、HBM2 和 HBM2e 一样,HBM3 依赖于每个堆栈 1024 个数据连接。 额外的速度来自每引脚 6.4 Gbps 的更高时钟频率。 最快的 HBM 2E 堆栈仍然达到每个引脚 3.6 Gbit/s 或每个堆栈 461 GB/s。 HBM3 规范现在可以堆叠 12 个 SDRAM 芯片,而不是之前的最多 8 个; 堆栈现在传输 819 GB/s,最多可容纳 24 GB。 2021 年 10 月,SK 海力士宣布推出首款 HBM-3 内存。

HBM 4

HBM 4 的交付时间已宣布为 2026 年。最初计划最多 12 个,后来计划最多 16 个堆叠芯片,这使得每个堆栈的内存大小高达 32 GB。 最大时钟速率为 5.6 GHz,这允许每个堆栈有足够的 1.4 TB/s。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/376283/