NMOS逻辑

编辑N型金属氧化物半导体逻辑使用n型来实现逻辑门和其他数字电路。这些nMOS晶体管通过在p型晶体管体中创建一个反转层而运作。这个反转层,称为n通道,可以在n型源极和漏极之间传导电子。n沟道是通过向第三个终端施加电压而形成的。与其他MOSFET一样,nMOS晶体管有四种工作模式:截止、三极管、饱和和速度饱和。

多年来,NMOS电路比可比的PMOS和CMOS电路快得多,后者不得不使用慢得多的p通道晶体管。制造NMOS也比CMOS容易,因为后者必须在p基板上的特殊n孔中实现p沟道晶体管。NMOS的主要缺点是,即使输出处于稳定状态,也必须有直流电流流经逻辑门。这意味着静态功率耗散,即即使在电路没有开关时也会有功率消耗。此外,就像二极管-晶体管逻辑、晶体管-晶体管逻辑、射极耦合逻辑等一样,不对称的输入逻辑电平使NMOS和PMOS电路比CMOS更容易受到噪声影响。这些缺点是为什么CMOS逻辑在大多数高速数字电路中取代了这些类型,如微处理器,尽管与用双极晶体管构建的逻辑门相比,CMOS最初非常缓慢。

NMOS逻辑的概述

编辑MOS是金属氧化物半导体的缩写,反映了MOS晶体管最初的构造方式,主要是在20世纪70年代之前,用金属(通常是铝)制成的栅极。然而,自1970年左右以来,大多数MOS电路都使用多晶硅制成的自对准栅极,这是飞兆半导体公司的费德里科-法金首先开发的技术。这些硅栅极仍然用于大多数类型的基于MOSFET的集成电路,尽管金属栅极(铝或铜)在21世纪初开始重新出现在某些类型的高速电路中,如高性能微处理器。MOSFET是n型增强模式晶体管,在逻辑门输出和负电源电压(通常是地)之间安排了一个所谓的下拉网络(PDN)。在正电源电压和每个逻辑门输出之间放置一个上拉。

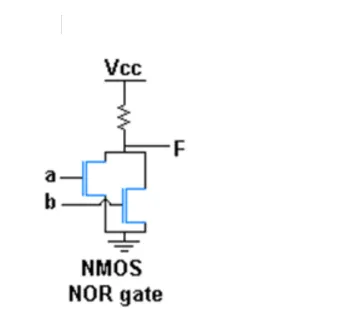

然后,任何逻辑门,包括逻辑反相器,都可以通过设计一个并联和/或串联电路的网络来实现,这样,如果布尔输入值的某个组合的所需输出为零(或假),PDN将处于激活状态,这意味着至少有一个晶体管允许在负电源和输出之间有电流路径。这将导致负载上的电压下降,从而在输出端产生低电压,代表零。作为一个例子,这里有一个NOR门以原理图NMOS实现。如果输入A或输入B是高电平,各自的MOS晶体管在输出和负电源之间充当一个非常低的电阻,迫使输出为低电平。当A和B都是高电平时,两个晶体管都是导电的,创造了一个更低的电阻路径到地。

输出为高电平的唯一情况是两个晶体管都关闭,这只发生在A和B都为低电平时,因此满足了NOR门的真值表。可以使一个MOSFET作为一个电阻工作,因此整个电路只能用n沟道MOSFET来做。NMOS电路从低电平过渡到高电平的速度很慢。当从高电平过渡到低电平时,晶体管提供低电阻,输出端的电容性电荷很快就耗尽了。但输出和正电源轨之间的电阻要大得多,所以低电平到高电平的转换需要更长的时间。使用一个低值的电阻会加快这个过程,但也会增加静态功率耗散。然而,一个更好的使栅极更快的方法是使用耗尽模式的晶体管而不是增强模式的晶体管作为负载。这被称为耗尽负载NMOS逻辑。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/171079/