核心存储器

编辑核心存储器使用硬磁材料(通常是半硬铁氧体)的环形(环)作为变压器磁芯,其中穿过磁芯的每根导线都用作变压器绕组。两根或多根电线穿过每个芯。磁滞允许每个核心“记住”或存储状态。

每个核心存储一位信息。磁芯可以顺时针或逆时针方向磁化。根据该磁芯的磁化方向,存储在磁芯中的位的值为零或一。通过磁芯的某些导线中的电流脉冲允许将该磁芯中的磁化方向设置为任一方向,从而存储一或零。通过每个核心的另一根线,即感测线,用于检测核心是否改变了状态。

读取核心的过程会导致核心重置为零,从而将其擦除。这称为破坏性读出。当不被读取或写入时,即使关闭电源,内核也会保持它们的最后一个值。因此它们是一种非易失性存储器。

使用更小的核心和电线,核心的存储密度缓慢增加,到1960年代后期,典型的密度约为每立方英尺32千比特(每升约0.9千比特)。然而,要达到这个密度,需要极其小心的制造,尽管多次努力使该过程自动化,但几乎总是手工进行。在此期间,成本从每比特约1美元下降到每比特约1美分。1960年代后期推出的第一个半导体存储芯片,最初创建了静态随机存取存储器(SRAM),开始侵蚀核心存储器市场。第一个成功的动态随机存取存储器(DRAM),英特尔1103,紧随其后的是1970年。它以每比特1美分的数量提供,标志着核心内存终结的开始。

半导体制造的改进导致存储容量的快速增加和每千字节价格的下降,而核心存储器的成本和规格变化不大。核心内存在1973年至1978年间逐渐退出市场。

阅读和写作

编辑为了读取内核存储器的位,电路尝试通过驱动在该内核处相交的选定X和Y线来将该位翻转到分配给0状态的极性。

- 如果该位已经为0,则内核的物理状态不受影响。

- 如果该位先前为1,则磁芯会改变磁极。这种变化在延迟后会在Sense线路中感应出一个电压脉冲。

检测到这种脉冲意味着该位最近包含一个1。没有脉冲意味着该位包含一个0。感测电压脉冲的延迟称为核心存储器的访问时间。

在任何这样的读取之后,该位包含一个0。这说明了为什么将核心内存访问称为破坏性读取:读取核心内容的任何操作都会擦除这些内容,并且必须立即重新创建它们。

要写入内核存储器的位,电路假定已经进行了读取操作并且该位处于0状态。

- 要写入1位,驱动选定的X和Y线,电流方向与读取操作相反。与读取一样,X线和Y线交叉处的磁芯会改变磁极性。

- 要写入0位(换句话说,禁止写入1位),同样量的电流也通过Inhibit线发送。这将流过相应内核的净电流减少到选择电流的一半,从而抑制极性变化。

访问时间加上重写时间就是内存循环时间。

Sense线仅在读取期间使用,Inhibit线仅在写入期间使用。出于这个原因,后来的核心系统将两者组合成一条线,并使用内存控制器中的电路来切换线的功能。

核心内存控制器的设计使得每次读取都紧跟在写入之后(因为读取强制所有位为0,并且因为写入假设这已经发生)。计算机开始利用这一事实。例如,内存中的值可以被读取和递增(例如通过PDP-6AOS上的指令)几乎与读取一样快;硬件只是增加了单个内存周期的读取阶段和写入阶段之间的值(可能向内存控制器发出信号,使其在周期中间短暂暂停)。这可能比通过读写周期获取值、增加某个处理器寄存器中的值、然后通过另一个读写周期写入新值的过程快两倍。

其他形式的核心内存

编辑字线核心存储器通常用于提供寄存器存储器。这种类型的其他名称是线性选择和二维。这种形式的核心存储器通常通过平面上的每个核心编织三根线,字读取、字写入和位检测/写入。读取或清除字,将全电流施加到一条或多条字读取线;这将清除选定的内核和任何翻转在其位感测/写入线中感应电压脉冲的内核。对于读取,通常只选择一个字读取线;但为了清楚起见,可以在位感测/写入时选择多个字读取线行被忽略。为了写入字,将半电流施加到一条或多条字写入线,并且将半电流施加到每条位感测/写入线以设置位。在某些设计中,字读取线和字写入线组合成一条线,从而形成一个每位只有两条线的存储器阵列。对于写入,可以选择多条字写入线。这提供了优于X/Y线重合电流的性能优势因为可以在单个周期内清除或写入相同值的多个字。典型机器的寄存器集通常只使用这种形式的核心内存的一个小平面。使用该技术构建了一些非常大的存储器,例如CDC6600中的扩展核心存储(ECS)辅助存储器,最多可容纳200万个60位字。

另一种形式的核心内存称为核心绳内存,提供只读存储。在这种情况下,具有更多线性磁性材料的磁芯被简单地用作变压器;实际上,没有信息以磁性方式存储在各个核心中。这个词的每一位都有一个核心。读取给定内存地址的内容会在对应于该地址的导线中产生电流脉冲。每条地址线要么穿过内核以表示二进制,要么绕在内核的外部以表示二进制。正如预期的那样,内核在物理上比读写内核内存大得多。

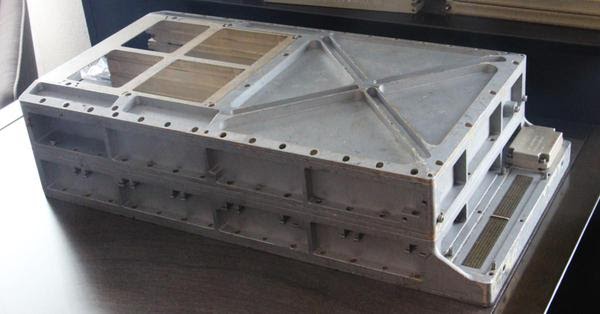

核心存储器的物理特性

编辑早期核心存储器的性能可以用今天的术语描述为与1MHz的时钟频率非常大致相当(相当于1980年代早期的家用计算机,如AppleII和Commodore64)。早期的核心内存系统的周期时间约为6µs,到1970年代初下降到1.2µs,到70年代中期下降到600ns(0.6µs)。一些设计具有更高的性能:CDC6600在1964年的内存周期时间为1.0µs,使用的内核需要200mA的半选择电流。为了减少访问时间和提高数据速率(带宽),我们尽了一切可能,包括同时使用多个核心网格,每个网格存储一个数据字的一位。例如,一台机器可能使用32个内核网格,每个内核中只有一个32位字,控制器可以在单个读/写周期内访问整个32位字。

核心内存是非易失性存储——它可以在没有电源的情况下无限期地保留其内容。它也相对不受EMP和辐射的影响。这些对于第一代工业可编程控制器、军事设施和飞行器等车辆以及航天器等应用来说是重要的优势,并导致在半导体MOS存储器(另请参见MOSFET)问世后使用核心多年.例如,航天飞机IBMAP-101B飞行计算机使用了核心内存,即使通过挑战者也保留了内存的内容’1986年解体并随后坠入海中。早期核心的另一个特点是矫顽力对温度非常敏感;一个温度下的正确半选电流不是另一温度下的正确半选电流。因此,内存控制器将包括一个温度传感器(通常是热敏电阻),以根据温度变化正确调整电流水平。DigitalEquipmentCorporation为其PDP-1计算机使用的核心存储器就是一个例子。这种策略在DEC为其PDP构建的所有后续核心内存系统中继续进行风冷计算机系列。另一种处理温度敏感性的方法是将磁芯“堆叠”封装在温度受控的烘箱中。这方面的例子是IBM1620的热空气核心内存(可能需要30分钟才能达到工作温度,大约106°F(41°C)和IBM7090的热油浴核心内存,早期的IBM7094和IBM7030。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/131692/