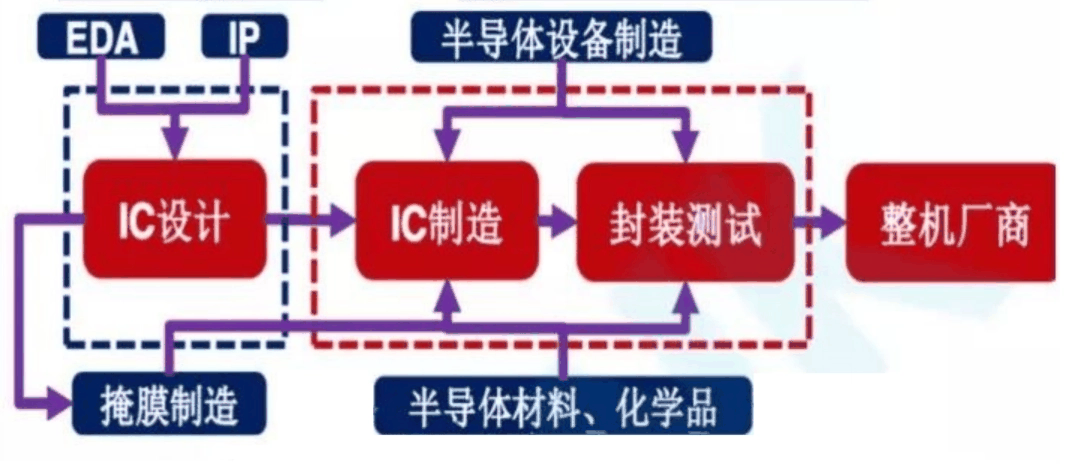

半导体IP核

编辑在电子设计中,半导体知识产权核心(SIP 核心)、IP 核心或 IP 块是逻辑、单元或集成电路布局设计的可重用单元,属于一方的知识产权。 IP 核可以授权给另一方或由单方拥有和使用。 该术语来自设计中存在的专利或源代码版权的许可。 专用集成电路 (ASIC) 和现场可编程门阵列 (FPGA) 逻辑系统的设计人员可以使用 IP 内核作为构建块。

历史

编辑IP 核在芯片设计中的许可和使用在 1990 年代成为普遍做法。 有许多许可方和许多代工厂在市场上竞争。

IP核的类型

编辑在芯片设计中使用 IP 核类似于使用库进行计算机编程或使用分立集成电路元件进行印刷电路板设计。 每个都是设计逻辑的可重用组件,具有已定义的接口和行为,已由其创建者验证并集成到更大的设计中。

软核

编辑IP 核通常以 Verilog 或 VHDL 等硬件描述语言中的可综合 RTL 形式提供。 这些类似于计算机编程领域中的 C 等低级语言。 作为 RTL 交付给芯片设计人员的 IP 内核允许芯片设计人员在功能级别修改设计,尽管许多 IP 供应商不对修改后的设计提供保证或支持。

IP 内核有时也作为通用门级网表提供。 网表是 IP 逻辑功能的布尔代数表示,实现为通用门或特定于过程的标准单元。 可以针对任何工艺技术编译作为通用门实现的 IP 核。 门级网表类似于计算机编程领域中的汇编代码列表。 网表为 IP 核供应商提供合理的保护,以防止逆向工程。 另见:集成电路布图设计保护。

网表和可综合内核都称为软内核,因为它们都允许综合、布局和布线 (SPR) 设计流程。

硬核

编辑硬核(或硬宏)是模拟或数字 IP 核,芯片设计人员无法对其功能进行重大修改。 这些通常被定义为特定于特定工艺技术的较低级别的物理描述。 硬核通常为其特定技术提供更好的芯片时序性能和面积的可预测性。

模拟和混合信号逻辑通常作为硬核分布。 因此,模拟 IP(SerDes、PLL、DAC、ADC、PHY 等)以晶体管布局格式(例如 GDSII)提供给芯片制造商。 数字 IP 核有时也以布局格式提供。

低级晶体管布局必须遵守目标代工厂的工艺设计规则。 因此,为一个代工厂的工艺交付的硬核不能轻易移植到不同的工艺或代工厂。 商业代工运营商(如 IBM、富士通、三星、TI 等)提供为自己的代工流程构建的各种硬宏 IP 功能,有助于确保客户锁定。

IP核来源

编辑许可功能

编辑许多最著名的 IP 内核都是软微处理器设计。 它们的指令集从小型 8 位处理器(例如 8051 和 PIC)到 32 位和 64 位处理器(例如 ARM 架构或 RISC-V 架构)各不相同。 这些处理器构成了许多嵌入式系统的大脑。 它们通常是 RISC 指令集,而不是像 x86 这样的 CISC 指令集,因为需要的逻辑更少。 因此,设计更小。 此外,x86 领导者英特尔和 AMD 大力保护其处理器设计的知识产权,并且不将这种商业模式用于其 x86-64 微处理器系列。

用于数字信号处理器 (DSP)、图形处理单元 (GPU) 的专用处理器。 随着工作负载超过主微处理器的能力,神经处理单元 (NPU) 和通用神经处理单元 (GPNPU) 变得流行起来。

IP 内核还获得了各种外围控制器的许可,例如 PCI Express、SDRAM、以太网、LCD 显示器、AC’97 音频和 USB。 其中许多接口都需要数字逻辑和模拟 IP 内核来驱动和接收芯片外部的高速、高压或高阻抗信号。

硬连线(与上述软件可编程软微处理器相反)数字逻辑 IP 核也被授权用于固定功能,例如 MP3 音频解码、3D GPU、数字视频编码/解码,以及其他 DSP 功能,例如 FFT、DCT 或维特比编码 。

内容由匿名用户提供,本内容不代表vibaike.com立场,内容投诉举报请联系vibaike.com客服。如若转载,请注明出处:https://vibaike.com/242826/